CPU的功能和基本结构

功能

- 指令控制:即程序顺序控制。完成取指令、分析指令、执行指令的操作

- 操作控制:管理由内存取出的指令,并产生操作信号送往相应部件,控制这些部件动作

- 时间控制:对操作的时间进行限制,为每条指令按时间顺序提供应有的控制信号

- 数据加工:对数据进行算术和逻辑运算

- 中断处理:对计算机运行的异常和特殊请求进行处理

基本结构

- 运算器:接受从控制器传来的命令并执行相应的动作,对数据进行加工、处理。组成为

- 算术逻辑单元(ALU):进行算术逻辑运算

- 暂存寄存器:暂存主存的数据,对应用程序员透明

- 累加寄存器(ACC):暂存ALU结果,也可以作为加法的一个输入

- 通用寄存器组:比如EAX、EBX等,详见第4章笔记的x86汇编指令入门

- 程序状态字寄存器(PSW):即条件码,如OF、SF、ZF、CF

- 移位器:对操作数或计算结果进行移位运算

- 计数器:控制乘除操作的步数

- 控制器:类型有硬布线控制和微程序控制器。作用是协调和控制计算机各部件执行程序指令序列,包括取指令、分析指令、执行指令,组成为

- 程序计数器(PC):存放下一条执行指令的地址,取指令时使用,有自增功能

- 指令寄存器(IR):保存正在执行的指令

- 指令译码器:对操作码译码, 给控制器提供特定操作信号

- 存储地址寄存器(MAR):存放要访问数据的内存地址

- 存储数据寄存器(MDR):存放要访问的数据

- 时序系统:产生时序信号,由时钟CLOCK分频得到

- 微操作信号发生器:根据IR、PSW和时序信号,产生控制整个计算机的控制信号,结构有

- 组合逻辑型:对应硬布线控制器

- 存储逻辑型:对应微程序控制器

- 寄存器

- 可以说CPU由运算器和控制器组成,事实上也可以说由运算器、控制器、寄存器组成

- 寄存器按用途分类

- 通用寄存器:比如EAX、EBX、ECX、EDX、ESI、EDI、EBP

- 专用寄存器:比如段寄存器(CS、DS、SS、ES、FS、GS)、EIP、PSW、IR、MAR、MDR

- 控制寄存器:CR0-CR3

- 栈顶寄存器ESP可以认为是通用寄存器或专用寄存器

- 寄存器按权限分类

- 用户可见寄存器:通用寄存器、PSW、EIP、段寄存器

- 用户不可见寄存器:MAR、MDR、IR、控制寄存器

指令执行过程

指令周期

- 从主存取出并执行一条指令的时间为指令周期

- 指令周期分为若干机器周期(CPU周期),不同指令不一定。

- 机器周期可以看作指令执行过程的基准时间

- 通常以最复杂指令功能的时间,即内存读一个指令字的最短时间作为机器周期(存取周期)

- 如果指令字长等于存储字长,则取指周期可以看作机器周期

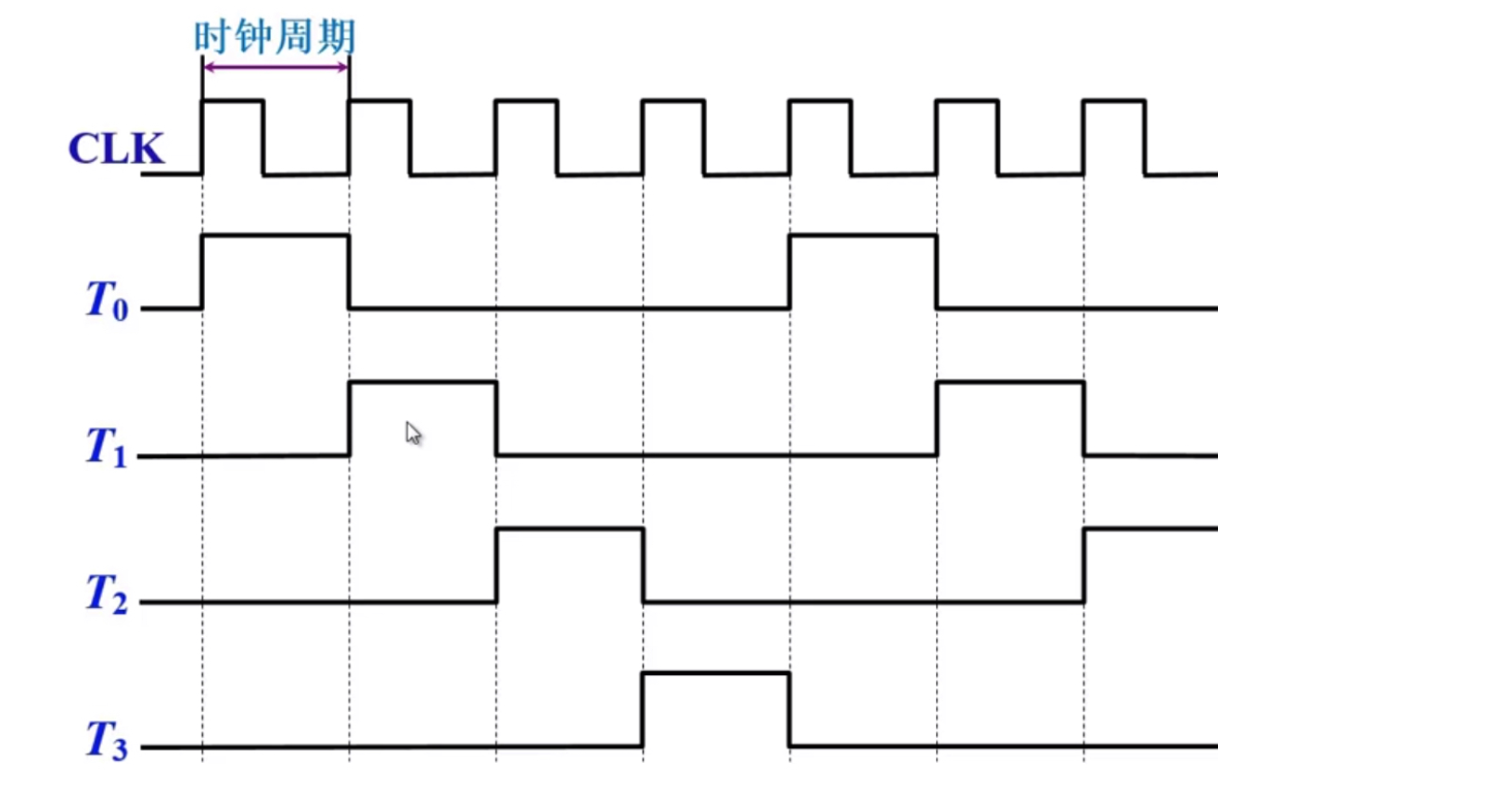

- 机器周期分为若干时钟周期(节拍、振荡周期)

- 每条微操作至少需要一个时钟周期

- 如果总线不冲突,多个微操作可以在一个周期内并行(后面详见数据通路小节)。

- 机器速度除了和主频有关,也和机器周期的时钟数、指令周期的机器周期数、是否采用流水线方式等有关

- 最完整的指令周期包括四个机器周期

- 取指周期:访存取指令、译码、更新PC

- 间指周期:访存取有效地址

- 执行周期:访存取操作数、执行操作

- 中断周期:访存保存程序断点、形成中断服务程序的入口地址、关中断

- 各种指令的指令周期

- 非访存指令

- 取指周期

- 执行周期

- 直接访存指令

- 取指周期

- 执行周期

- 间接访存指令

- 取指周期

- 间指周期

- 执行周期

- 转移指令

- 取指周期

- 执行周期

- 间接转移指令

- 取指周期

- 间址周期

- 执行周期

- 非访存指令

- 4个标志触发器用来区分四个机器周期,为1表示状态有效

- FE:fetch

- IND:indirect

- EX:execute

- INT:interupt

指令周期的数据流

取指周期

- 任务是根据PC取指令放到IR中

- 数据流如下:

- 发送指令地址给主存:PC->MAR->地址总线->主存

- 发送读信号给主存:CPU控制器->控制总线->主存

- 接收主存的指令数据:主存->数据总线->MDR->IR

- 更新程序计数器:默认是PC+1

间指周期

- 任务是取操作数的有效地址

- 数据流如下(以一次间址为例)

- 发送间接地址给主存:IR(地址字段)->MAR->地址总线->主存(若是多次间址,也可以是MDR->MAR->地址总线->主存)

- 发送读信号给主存:CPU控制器->控制总线->主存

- 接收主存的有效地址:主存->数据总线->MDR->IR

执行周期

- 任务是根据操作码和操作数通过ALU产生执行结果

- 不同指令执行周期的数据流不一定

中断周期

- 任务是处理中断请求,需要保存程序断点

- 数据流如下

- 控制器发送减1后的ESP给主存:ESP->MAR->地址总线->主存

- 发送写信号给主存:CPU控制器->控制总线->主存

- 程序断点存入主存:PC->MDR->数据总线->主存

- 更新PC:CPU控制器(中断程序入口)->PC

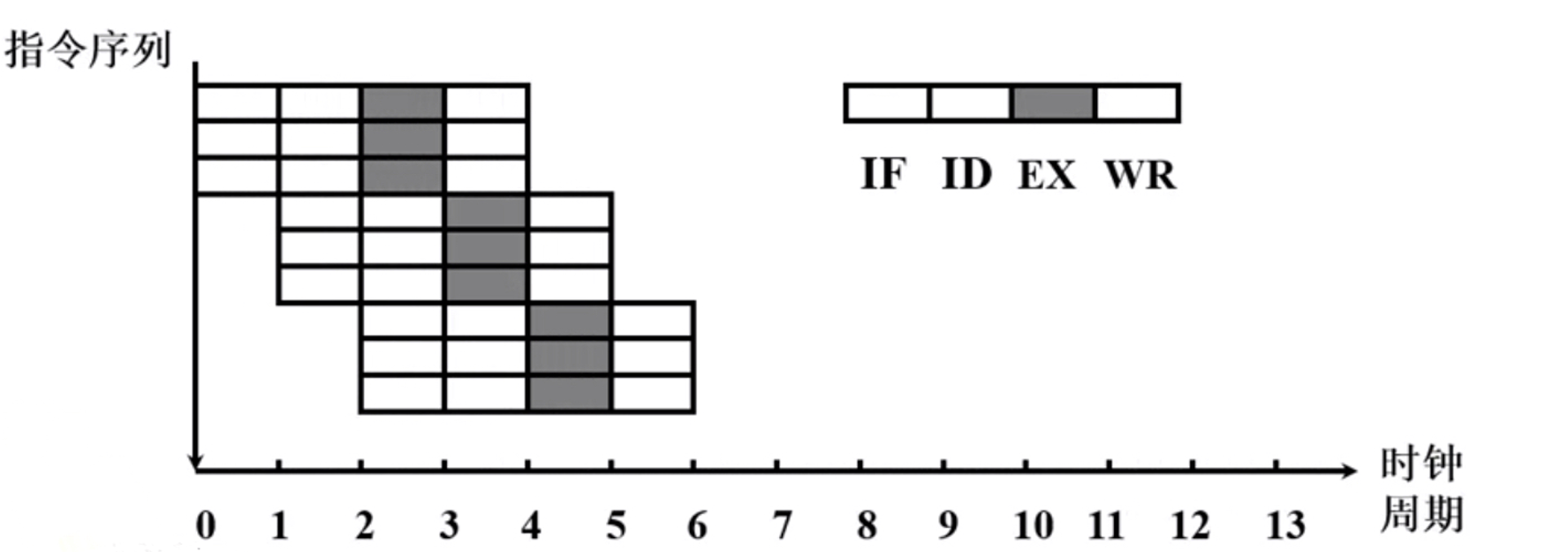

指令执行方案

- 单指令周期

- 对所有指令选用相同的执行时间完成,指令周期取决于耗时最长的指令

- 每个指令需要的时钟周期数固定

- 前一条指令完成后,下一条指令才能开始,即串行执行

- 多指令周期

- 对不同指令用不同执行步骤完成,不要求执行时间相同

- 不同指令的时钟周期数可不同

- 前一条指令完成后,下一条指令才能开始,即串行执行

- 流水线方案

- 指令之间并行执行,理想情况是每个时钟周期都能有一条指令完成

- 在每个时钟周期启动一条指令,多个指令同时运行,各自处于不同执行的步骤

数据通路

基本概念

- 数据通路指的是功能部件之间传送数据的路径

- 功能部件有例如:ALU、通用寄存器、状态寄存器、异常中断处理逻辑等

- 通路的建立由控制信号控制,控制信号来自控制单元CU的输出端

- 每个时钟周期内控制信号认为是不变的

- 部件名称加上op后缀,表示操作选择控制信号

- 部件名称加上in或out后缀,表示允许输入或允许输出控制信号

- 寄存器的允许输入信号in具体的可以叫写使能信号,受时钟驱动,因为寄存器是由触发器组成

- 对应器件有时钟端口

- 每个时钟周期到来的时候,寄存器的值更新

- 允许输出控制信号out所控制的部件称为三态门,不受时钟驱动

- 信号高天平表示单向输出

- 信号低电平表示阻断

- 内存读写的控制信号也受到时钟控制

- PC自动更新受到控制信号PC+1的控制

- CPU中有一个多路选择器的一端输入是常数,大小是PC自动更新的字节数

- 一般用BUS表示数据总线

基本结构

- CPU内部单总线方式:CPU中连接各部件的总线只有一条,结构简单但传输容易冲突,需要用到锁存器,是早期的选择

- CPU内部多总线方式:CPU中有多条总线,也可以是具体指出二总线、三总线。总线数越多,需要的锁存器(暂存器)越少,需要的周期数越少,成本越高。

- 专用数据通路方式:不共享总线,根据数据通路情况设置专用的线路,现代计算机主要选择

微操作序列

- 使用微操作序列可以描述具体的取指令、译码、执行指令过程中的数据流向

- 一般分两列写

- 第一列的每行是每个周期(节拍)进行的微操作(用箭头指出数据流向,详见控制器功能的微操作命令分析)

- 若没有总线冲突,每行可以有多个微操作。

- 第二列的每行是微操作对应的控制信号情况

- 控制信号需要考虑的有in信号、out信号、op信号、PC+1信号、内存读信号R、内存写信号W

控制器的功能和基本原理

微操作命令分析

取指周期

- PC->MAR->DB(PC传给地址寄存器,传给数据总线)

- 1->R(读信号传给内存储器)

- M(MAR)->MDR(内存中读指令到数据寄存器)

- MDR->IR(指令放到IR中)

- OP(IR)->CU(指令操作码给CU进行译码)

- (PC)+1->PC(更新PC)

间址周期

- Ad(IR)->MAR(指令地址码给数据寄存器)

- 1->R(读信号传给内存储器)

- M(MAR)->MDR(内存中读有效地址到数据寄存器)

- MDR-> Ad(IR)(有效地址传给IR)

执行周期

- 非访存指令

- CLA(清空ACC):

- COM(取反ACC):

- SHR(算术右移):

- CSL(循环左移):

- STP(停机指令):

- CLA(清空ACC):

- 访存指令

- ADD X(加法指令):

- STA X(存数指令):

- LDA X(取数指令):

- ADD X(加法指令):

- 转移指令

- JMP X(无条件转移):

- BAN X(条件转移之最近的计算结果是负则转):

- JMP X(无条件转移):

中断周期

- 保存程序断点

- 程序断点存入"0"地址

- 0->MAR

- 1->W

- PC->MDR

- MDR->M(MAR)

- 程序断点进栈

- (SP)-1->MAR

- 1->W

- PC->MDR

- MDR->M(MAR)

- 程序断点存入"0"地址

- 形成中断服务程序的入口地址

- 硬件向量法:向量地址->PC

- 软件查询法:中断识别程序入口地址M->PC

- 关中断

- 0->EINT

控制器结构和功能

- 不同于CPU内总线,系统总线用于连接计算机硬件系统五大部件,包括控制器、运算器、存储器、输入输出

- 系统总线分为

- Data Bus 数据总线

- Address Bus 地址总线

- Control Bus 控制总线

- 五大部件和系统总线的连接结构

- 控制器

- DB到MDR到IR:从DB接收指令信息

- PC到MAR到AB:把指令地址送到AB

- CU到CB:控制单元CU通过CB提供控制信号给其他部件

- 运算器到PC:从运算器接收指令转移地址

- 运算器:连向数据总线,以和内存、输入、输出设备传送数据

- 存储器(指内存)、输入设备、输出设备

- 用DB传送数据

- 从AB接收地址

- 从CB接收控制信号

- 输入输出设备需要通过接口和总线相连

- 控制器

- 控制器的功能

- 取指令(从主存),并指出下一条指令地址

- 译码,产生相应操作控制信号

- 执行指令,指挥并控制CPU、主存、IO的数据流向

- 控制器的两种分类(PC和IR相同;指令执行步骤的确定方法和控制信号的给出方案不同)

- 硬布线控制器

- 微程序控制器

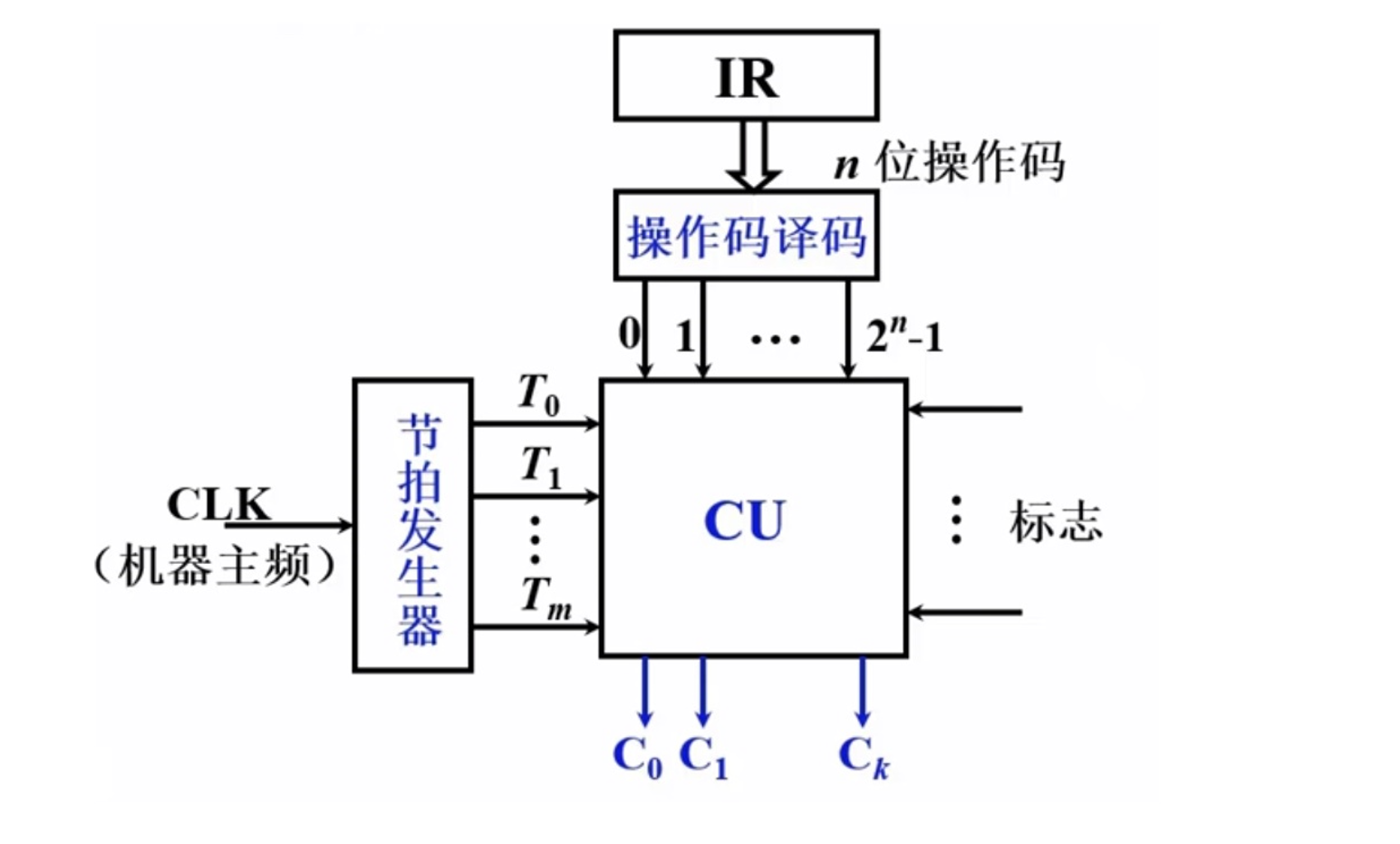

控制单元的功能

- 输入

- IR的操作码在经过译码产生的指令信息

- 时钟信号。每个时钟脉冲CU发出一个(或一组同时执行的)操作命令

- 标志,即执行单元的反馈信息。比如条件转移指令的控制。

- 来自系统总线的控制信号,如中断请求,DMA请求,HRQ总线请求

- 输出

- CPU内部控制信号,如

- 到系统控制总线的控制信号

- 访存控制信号

- 访IO/存储器控制信号

- 读内存命令

- 写内存命令

- 中断响应信号

- 访存控制信号

- CPU内部控制信号,如

控制方式

- 同步控制方式

- 任一微操作由统一基准时标的时序信号控制

- 以最长的微操作序列、最复杂的微操作作为标准

- 采取完全统一的、相同时钟周期数、相同时间间隔的机器周期运行不同指令

- 异步控制方式

- 无基准时标信号

- 无固定的周期节拍,无严格的时钟同步

- 采用应答方式联络

- 联合控制方式

- 同步和异步结合

- 大部分指令的微操作同步控制,少部分指令的微操作异步控制

- 人工控制方式

- Reset

- 连续或单条指令的执行转换开关

- 符合条件即停机开关

硬布线控制器

又叫组合逻辑控制器 #### 单元框图

- 输出

- 同时为1的输出信号表示对应操作可以在一个周期内完成

- 时钟信号控制节拍发生器产生节拍

- 节拍宽度等于时钟周期,每个节拍内机器完成一个或几个同时执行的操作

- 如下图的例子,一个机器周期,包括了四个节拍

单元设计步骤

- 列出微操作的操作时间表。表中每一行说明了在各个机器工作周期、节拍下,包含该行微操作命令信号的指令(硬件实现上操作码表示指令)的情况

- 微操作信号综合。微操作控制信号=该微操作对应的所有行的逻辑表达式的或,每行逻辑表达式=机器周期 and 节拍 and 脉冲 and 操作码 and 机器状态条件

- 绘制微操作命令逻辑图。即根据上一步的逻辑表达式绘制出每个微信号的逻辑电路图,使用逻辑门电路实现。

微程序控制器

又叫存储逻辑控制器

基本概念

- 微程序

- 把机器指令编写成微程序

- 每条机器指令对应一个微程序

- 所有微程序存放在控制存储器中,寻址方法同用户程序寻址

- 各个机器指令的执行周期编写为各自的微程序

- 取值周期、间址周期和中断周期单独编写为微程序(都是不同机器指令的公共微程序)

- 公共微程序中的取值微程序是必须的,即n条机器指令至少需要在控制寄存器中存入n+1个微程序

- 微程序有若干微指令

- 每个微指令有若干微命令

- 微程序是计算机设计者事先编址并放在控制存储器中的,对程序员透明

- 把机器指令编写成微程序

- 微命令

- 前面提到过微操作是计算机中最基本的不可分解的操作

- 微命令和微操作一一对应,指的是微操作的控制信号

- 微操作是微命令的执行过程

- 硬布线控制器中也有微命令的概念,不是微程序控制器中独有的概念

- 微指令

- 前面提到过,如果每个节拍内的微命令线路不冲突,则可以并行执行(相容微命令)

- 不可同时产生和完成的微命令是互斥微命令

- 这些并行的微命令可以合并成一条微指令,一个节拍对应一条微指令

- 微指令基本格式

- 操作控制字段(微操作码字段):产生各自微操作控制信号

- 顺序控制字段(微地址码字段、下地址字段):产生下一条待执行的微指令的地址

- 控制存储器:相比于CPU外部的,用RAM实现的主存储器,控制存储器CM在CPU内部(控制器的CU里),用ROM实现

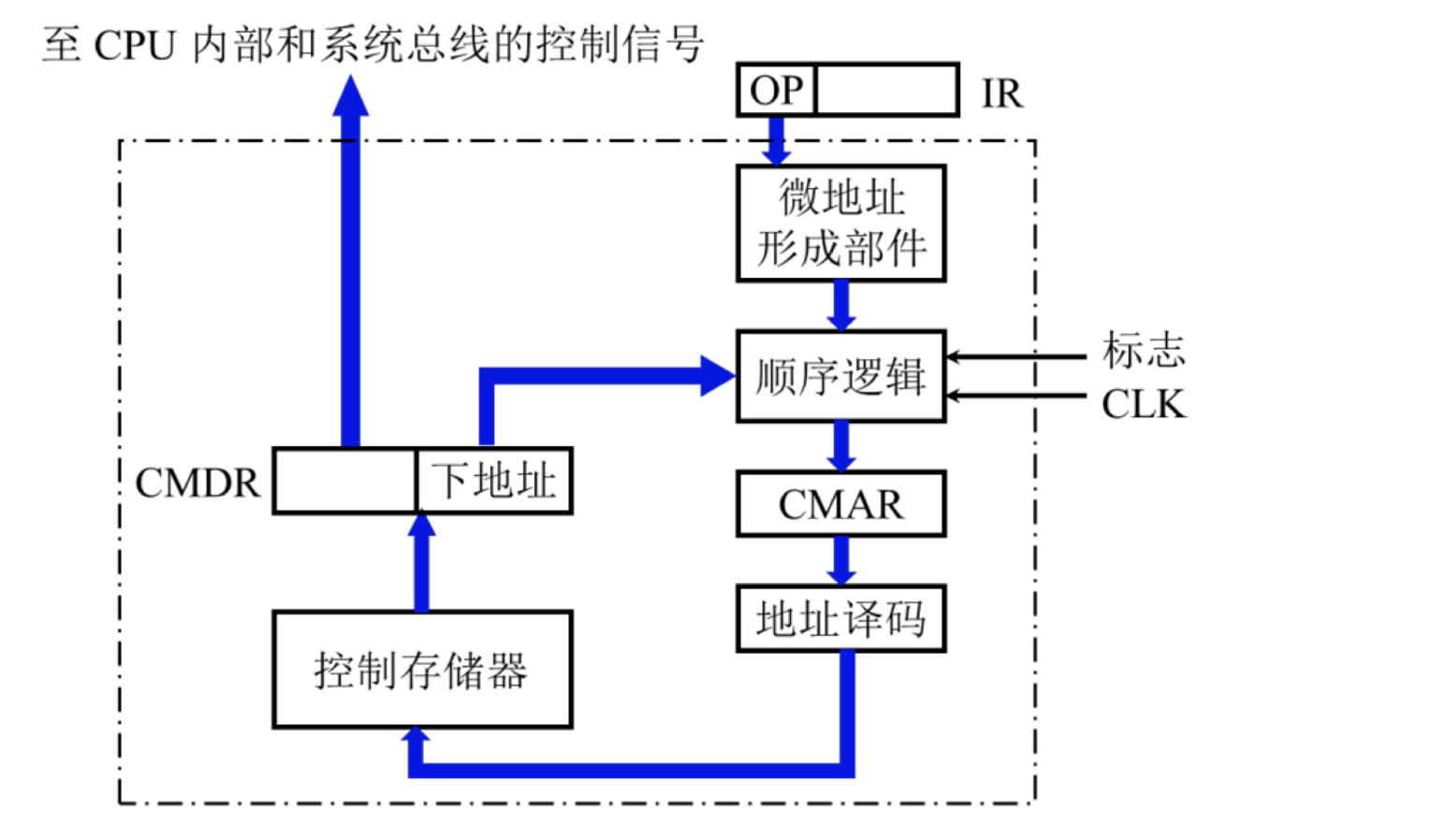

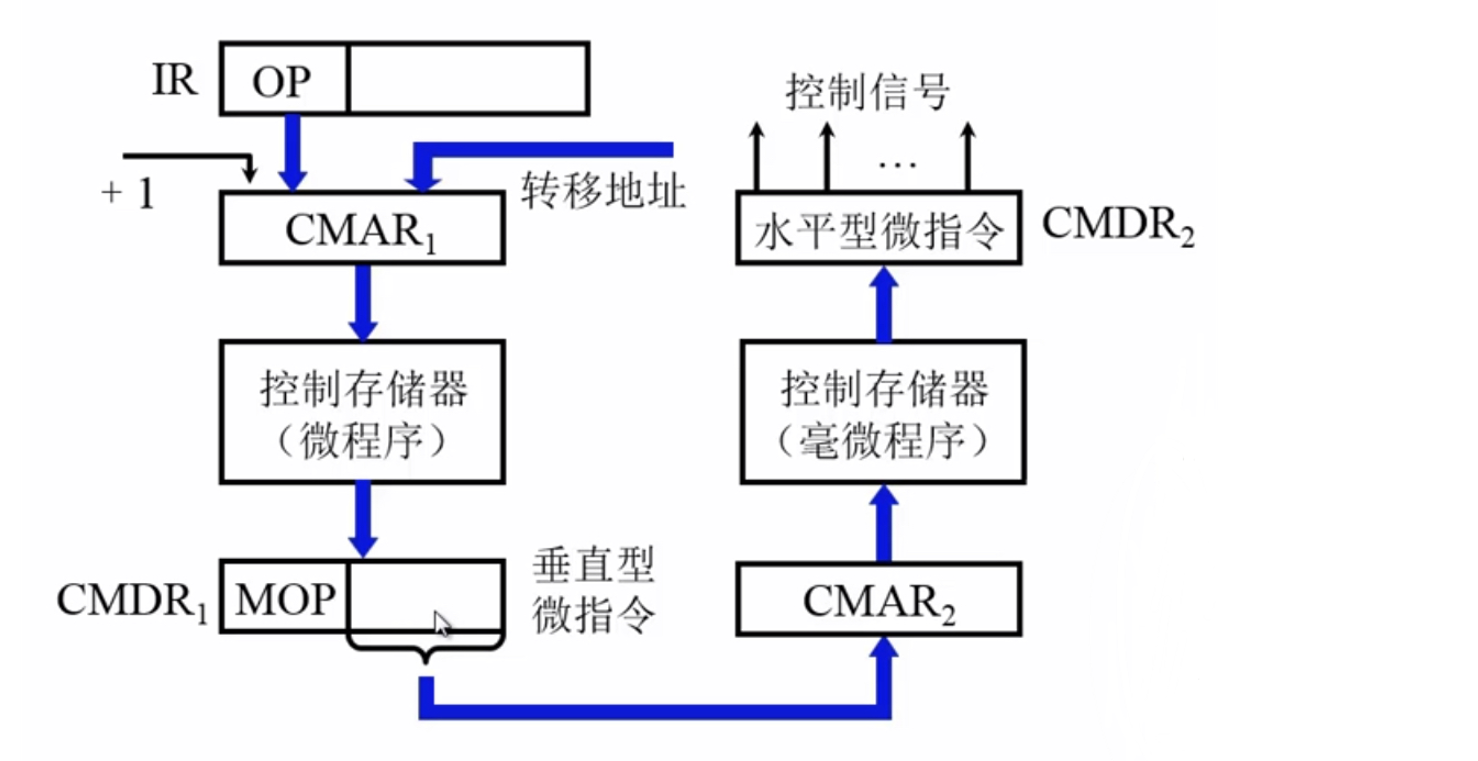

单元框图

- 下图是微程序控制器的CU框图

- 包括

- 控制存储器CM:存放微程序,由ROM构成

- 控制存储器地址寄存器CMAR(也叫微地址寄存器):存放微指令的地址

- 控制存储器数据寄存器CMDR(也叫微指令寄存器μIR):存放控制寄存器中取出的微指令

- 微地址形成部件:产生初始微地址和后继微地址

- 顺序逻辑:根据时钟、标志、CMDR,从微地址形成部件中选出正确的地址,传给CMAR

工作过程

- 运行公共微程序,比如取指微程序

- 将取指微程序的入口(一般是CM的0号单元)送到CMAR

- 从CM中读出微指令送入CMDR

- 微程序完成后,主存中的机器指令存入了IR中

- 微地址形成部件根据机器指令操作码字段产生对应微程序入口地址,送入CMAR

- 从CM中读出微指令送入CMDR,并执行

- 执行完一个机器指令对应的微程序,回到第一步,继续进行公共微程序,取指微操作。

微指令编码方式

- 又叫微指令控制方式,对应微指令操作控制字段的编码方式,以形成控制信号

- 分类为

- 直接编码方式(直接控制方式)

- 每一位表示一个微命令是否有效,可以直接发出控制信号

- 简单直观并行性好,但微指令字长过长

- 字段直接编码方式

- 把微指令分成各个小字段,每小字段经过译码后才能发出(一个)控制信号

- 互斥微命令(在一个互斥类中)放到一个小字段中,显式编码(每小字段位数不能太多,否则译码太慢)

- 相容微命令放到不同的小字段中,各小字段编码单独定义

- 可以缩减微指令字长,但需要译码才能发出微命令,速度慢

- 注意,比如某小字段有3位,只能表示8-1=7个互斥的微命令,因为需要留一个状态表示不进行微操作。

- 字段间接编码方式(隐式编码方式)

- 一个字段的某些微命令需要由另一个字段某些微命令解释

- 进一步缩短微指令字长,但是削弱了并行控制能力

- 混合编码

- 直接编码间接编码混合使用

- 字段间接编码一般是字段直接编码的辅助手段

- 直接编码方式(直接控制方式)

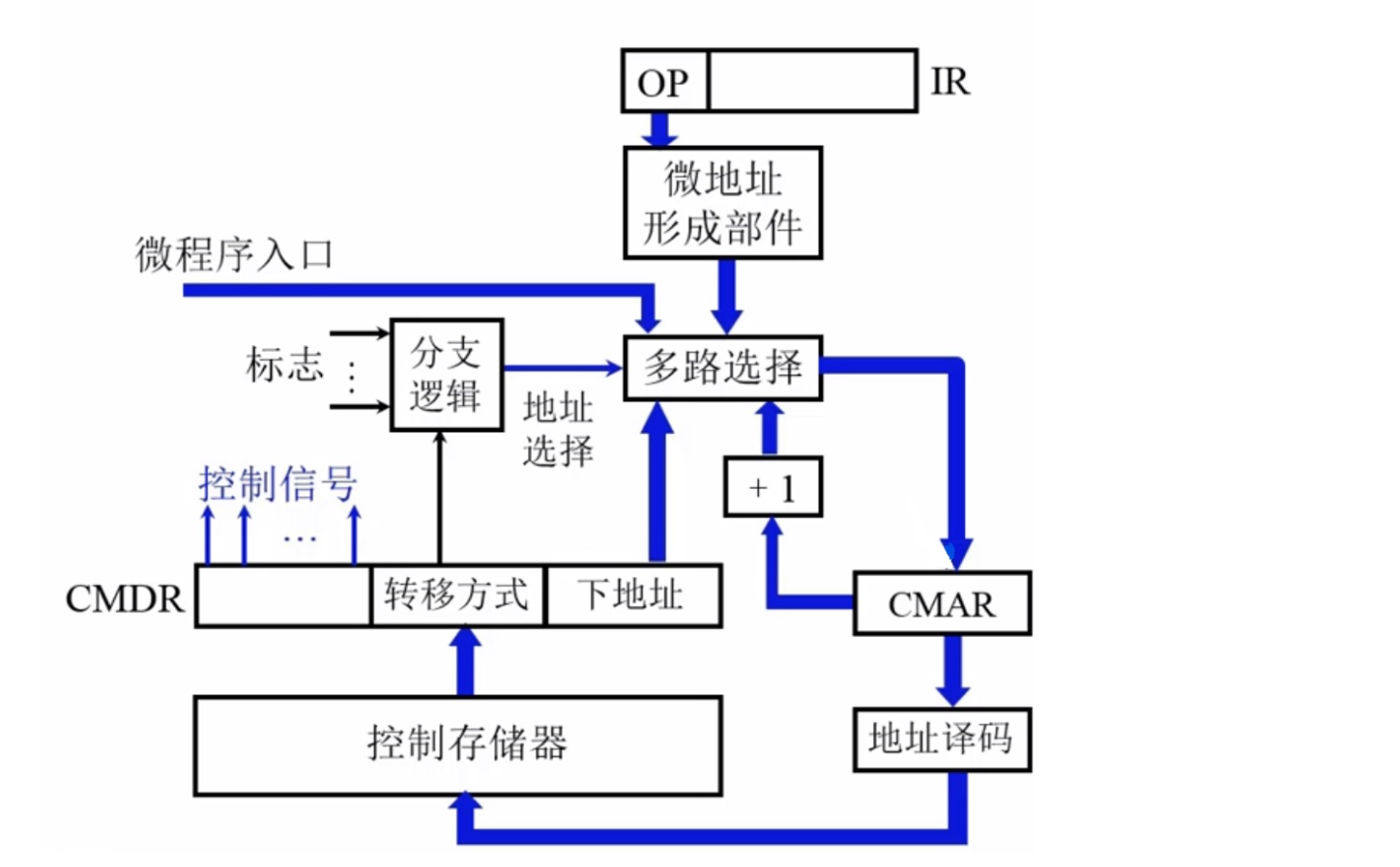

微指令地址形成方式

- 基本方式

- 由微指令的下地址字段指出,称为断定方式

- 有时下地址字段没有指出,可以根据机器指令的操作码,经过微地址形成部件形成(该机器指令操作微程序的首地址)

- 补充方式

- 增量计数器法,即(CMAR)+1->CMAR,适合后继指令地址连续的情况

- 分支转移法

- 把顺序控制字段进一步划分为转移方式的标志和转移地址(下地址)

- 标志为0表示不跳转,执行(CMAR)+1->CMAR

- 标志为1表示跳转,根据转移地址确定下一条微指令地址

- 测试网络法

- 把下地址字段进一步划分为高位字段和低位字段

- 低位字段由测试源(状态、条件)经过测试网络进行变换,得到测试地址;高位字段不变,作为非测试地址

- 非测试地址和测试地址拼接,形成下一条微指令地址

- 适合微程序小范围的微指令跳转

- 由硬件直接产生微程序入口地址

- 电源通电后,第一条微指令地址(取指微程序入口地址)可以由专门硬件电路产生

- 如果有中断或间址周期,其微程序首地址可以由硬件产生

- 根据微指令地址形成方式,把CU框图的顺序逻辑展开,如下图

微指令格式

- 水平型微指令

- 格式为操作控制、顺序控制(包括判断字段、后地址字段)

- 一次能定义并执行多个并行操作

- 比如直接编码、字段直接编码、字段间接编码、混合编码

- 优点是灵活性强、可并行、微程序短、每条微指令执行时间短、不需要译码或需要简单译码

- 和机器指令差别大

- 垂直型微指令

- 类似于机器指令操作码的方式:微操作码、 目的地址、源地址

- 一次只能定义和执行一个基本操作

- 优点是格式简单规整、编写微程序方便、微指令短

- 接近机器指令

- 混合微指令

- 以垂直型为基础,增加不复杂的并行操作

- 便于编程、微程序不长、执行速度有所提高

静态微程序设计和动态微程序设计

- 静态:微程序无需改变,采用ROM

- 动态:通过改变微指令和微程序改变机器指令,利于仿真、采用EPROM

毫微程序设计

- 微程序设计:用微程序解释机器指令

- 毫微程序设计:用毫微程序解释微指令

- 毫微程序设计本质上是一种二级结构

- 毫微程序放在毫微控制器中

- 毫微程序由毫微指令组成,由毫微指令来控制硬件

- 二级结构中毫微指令一般是水平型,微指令一般是垂直型

- 毫微程序控控制器的基本组成如下图

微程序控制方式

- 串行微程序控制:串行方式

- 并行微程序控制:流水方式

单元设计步骤

- 写出对应机器指令的微操作和节拍安排

- 微操作命令需要由CMDR的操作字段分析后发出控制信号

- 在之前微操作分析的基础上,在每条微操作前增加把下一条微指令地址送到CMAR的微操作

- 比如取指阶段的微操作序列为

- 节拍0:PC->MAR,1->R(本节拍微操作的微指令地址可以由硬件生成)

- 节拍1:Ad(CMDR)->CMAR(把下一节拍的微指令的地址送到CMAR)

- 节拍2:M(MAR)->MDR,(PC)+1->PC

- 节拍3:Ad(CMDR)->CMAR(把下一节拍的微指令的地址送到CMAR)

- 节拍4:MDR->IR

- 节拍5:OP(IR)->微地址形成部件->CMAR(把下一机器周期第一个节拍的微指令地址送到CMAR)

- 确定微指令的格式,包括

- 微指令编码方式:根据微操作个数确定编码方式和操作控制字段位数

- 后继微指令地址形成方式:根据控制存储器的微指令个数确定顺序控制字段位数

- 微指令字长:操作控制字段和顺序控制字段位数确定微指令字长

- 编写每条微指令的码点(每条微指令的具体编码和在控制存储器中的位置)

硬布线和微程序控制器对比

- 工作原理

- 硬布线控制器由组合逻辑电路根据当前的指令码、状态、时序,即时产生微操作控制信号

- 微程序控制器以微程序的方式,通过存储在控制存储器的微指令产生微操作控制信号

- 执行速度

- 硬布线控制器快

- 微程序控制器慢

- 规整性

- 硬布线控制器繁琐

- 微程序控制器规整

- 应用场合

- 硬布线控制器应用于RISC CPU

- 微程序控制器应用于CISC CPU

- 易拓展性

- 硬布线控制器难修改

- 微程序控制器容易扩充、修改

异常和中断机制

基本概念

- 程序中断指的是计算机执行程序时,出现某些急需处理的异常或特殊请求,CPU暂时中断现行的程序,对异常情况或特殊请求进行处理,处理完后再返回原程序断点处继续执行。

- 程序中断的作用有

- 实现CPU和IO的并行

- 处理硬件故障、软件错误

- 实现人机交互

- 实现多道程序的切换、分时操作等

- 实现实时处理

- 实现用户态到内核态的切换,即(广义的)软中断

- 多处理器系统的处理器信息交流和任务切换

分类

- 广义上的中断包含内部中断和外部中断

- 内部中断包括软件中断(狭义的软中断)和异常(内中断一定是不可屏蔽中断),外部中断包括可屏蔽中断和不可屏蔽中断

- 软件中断指的是CPU内部的指令请求

- 又叫可编程中断,是软件主动发起的中断

- 软件中断实现从用户态到内核态的系统调用,完成后回到中断指令的下一条继续运行

- 比如linux的int 0x80系统调用

- 异常指的是CPU内部异常产生的意外事件,包括

- 故障Fault

- 程序性事故

- 比如溢出、非法操作码、除数为0、缺页

- 故障被动性的导致用户态切换到内核态,故障是有可能修复处理的,比如缺页处理后可以继续执行

- 修复完成后从出故障的指令处重新运行(而不是运行下一条指令)

- 陷阱Trap

- 人为设置的中断,又叫自陷

- 主要用于断点调试

- 执行Trap指令主动导致用户态切换到内核态,处理完陷阱后会返回用户态继续执行下一条指令

- 终止Abort

- 当指令发送不可修复的故障,程序只能终止

- 操作系统把程序的进程从进程表去除

- 故障Fault

- 外部中断简称外中断,是狭义上的中断,指的是CPU外部和指令执行无关的事件引起的中断,包括

- 可屏蔽中断:通过INTR(Interrupt Require)信号线发出的中断请求,受到中断允许寄存器和中断屏蔽位的控制(后面会介绍两者的功能和区别),比如IO设备中断(键盘输入、打印机缺纸)

- 不可屏蔽中断:通过NMI(Nonmaskable Interrupt)信号线发出的中断请求,比如电源掉电、内存读写错误、总线奇偶校验错误、时钟中断

检测和响应

中断请求

中断源如何提出中断请求

- 外中断请求的识别一般由硬件完成

- 每个中断源设置一个INTR中断请求触发器,1位,表示是否请求中断

- INTR可以分散在各个中断源接口电路

- INTR也可以集中在CPU内部中断系统中,由多个INTR触发器组成中断请求寄存器

- 内中断请求的识别一般由软件完成

- CPU设置一个异常状态寄存器

- 操作系统使用统一的异常查询程序,按一定优先级查询异常状态寄存器

- 先查询到的先被处理

- 软中断、故障、陷阱等内中断请求也可以不通过专门的查询程序识别,而是在某指令执行时识别,转到内核态进行异常处理

中断判优

多个中断源同时提出中断请求时如何进行优先级排队

- 硬件实现的排队器,具体有两种做法

- 链式排队器:分散在各个中断源的接口电路中

- 集中在CPU内

- 软件实现的排队器,用程序查询的方式

- 先查询高优先级的中断源是否有中断请求

- 是则跳转到对应中断服务程序入口地址,否则继续查询低优先级中断源是否有中断请求

- 通常的优先级安排如下:

- 硬件故障优先级最高,其次是软件中断,这些都是不可屏蔽中断

- 不可屏蔽中断优先级高于可屏蔽中断(可屏蔽中断一定是外中断,但不是所有外中断都可屏蔽)

- DMA请求优先级高于IO设备的中断请求,高速设备优先于低速设备、输入设备优先于输出设备、实时设备优先于普通设备

响应条件

CPU什么条件下响应(外)中断

- 中断源发出中断请求,即存在中断请求触发器INTR为1的中断源(INTR的设置要求中断源的中断屏蔽触发器为0,详见后面多重中断部分)

- CPU允许中断(允许中断触发器EINT=1),即开中断(linux中是中断标志IF=1)

- 一条指令执行完毕时,且没有更紧迫任务(比如内中断)

响应操作

CPU响应(外)中断具体要进行的操作是什么

- CPU响应中断时完成的操作是中断隐指令

- 中断隐指令由硬件实现,并不是真的指令系统的指令

- 中断隐指令包括的操作有

- 关中断

- 如果有中断请求(INTR不全为0)且允许中断(EINT=1),则中断标记触发器INT设置为1,表示进入中断周期(在前面指令周期的笔记中提到过INT),此后EINT设置为0

- 关中断保证不响应更高级别的可屏蔽中断,但不可屏蔽中断依然需要响应

- 保存断点:包括PC和PSW的现场信息

- 转向中断服务程序:取出中断服务程序的入口地址传给PC

- 关中断

中断入口

如何确定中断服务程序的入口地址

- 中断向量:中断服务程序的入口地址

- 中断向量地址:中断服务程序入口地址所存放的地址

- 中断向量表:存储器中集中存放中断向量的区域

- 硬件向量法

- 把中断优先级排队器输出,输入到向量地址形成部件,得到中断向量地址

- 根据中断向量地址到中断向量表中确定中断向量,即入口地址

- 软件查询法:PC先转到中断识别程序入口地址,由中断识别程序给出中断入口地址,灵活,识别程序相比硬件实现更容易修改

处理过程

进入中断周期后的处理过程

- 硬件(中断隐指令)完成的过程

- 关中断

- 保存断点

- 转向中断服务程序

- 中断服务程序完成的过程

- 保存现场和屏蔽字

- 现场主要是一些工作寄存器,PUSH到堆栈中

- 屏蔽字在后面的多重中断的笔记中会介绍

- 开中断:允许更高级别的中断响应,实现中断嵌套

- 执行中断服务程序:中断请求的目的

- 关中断:保证恢复现场和屏蔽字时不被打断

- 恢复现场和屏蔽字:从堆栈中POP出

- 开中断

- 中断返回:一般是中断服务程序的最后一条指令IRET,用于返回原程序继续执行

- 保存现场和屏蔽字

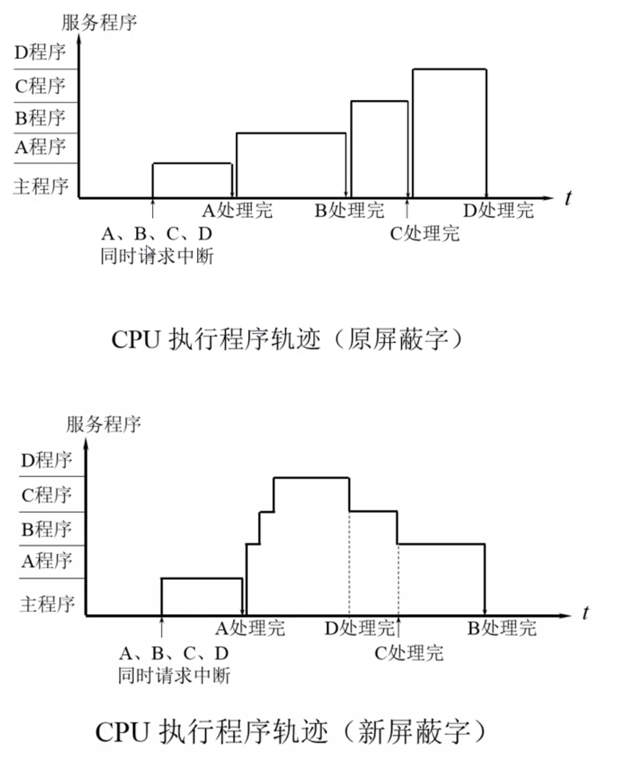

多重中断

在执行中断服务程序时又出现新的更高级别的中断请求怎么办

- 单重中断:不响应新的中断请求

- 多重中断:响应新的中断请求,又叫中断嵌套

- 多重中断使用中断屏蔽技术

- 每个中断源有一个中断屏蔽触发器,表示是否屏蔽该中断源,屏蔽后INTR无法置1

- 所有中断屏蔽触发器组合构成一个屏蔽字寄存器,不同的中断服务程序运行时,屏蔽字寄存器的内容不同(该内容是根据中断源优先级设置屏蔽字的)

- 屏蔽字寄存器的内容叫做屏蔽字

- 中断允许寄存器和中断屏蔽字寄存器的功能区别

- 前者是总的中断的允许开关,决定CPU在有中断请求时是否进入中断周期

- 后者是对中断源之间的优先级关系的表示。高优先级中断源的中断服务程序运行时,低优先级的中断源在屏蔽字寄存器中所对应位(即低优先级中断源屏蔽触发器)为1,表示屏蔽掉对应优先级较低的中断请求

- 多重中断需要满足的条件

- 中断允许寄存器满足的条件:在中断服务程序中设置开中断

- 中断屏蔽字寄存器满足的条件:仅较高优先级的中断源有权中断较低优先级的中断源

- 中断响应排队优先级和中断源处理优先级的区别

- 中断响应排队优先级不可改变

- 中断源处理优先级可以通过重设屏蔽字来改变

- 例如下面两个图,表示ABCD四个中断请求同时到来后的响应情况。排队优先级按ABCD降序,处理优先级第一个图为ABCD降序,第二个图改为ADCB降序

指令流水线

基本概念

- 一条指令的执行分为若干阶段,每个阶段用到的功能部件不同。将各个阶段看作流水段(对应一个部件),指令的执行过程构成了指令流水线

- 指令流水线是一种硬件层面的并行处理技术(进程的并行属于软件层面的并行处理技术),能明显提高计算机运行速度

- 指令流水线不包含生成控制信号的控制部件

基本实现

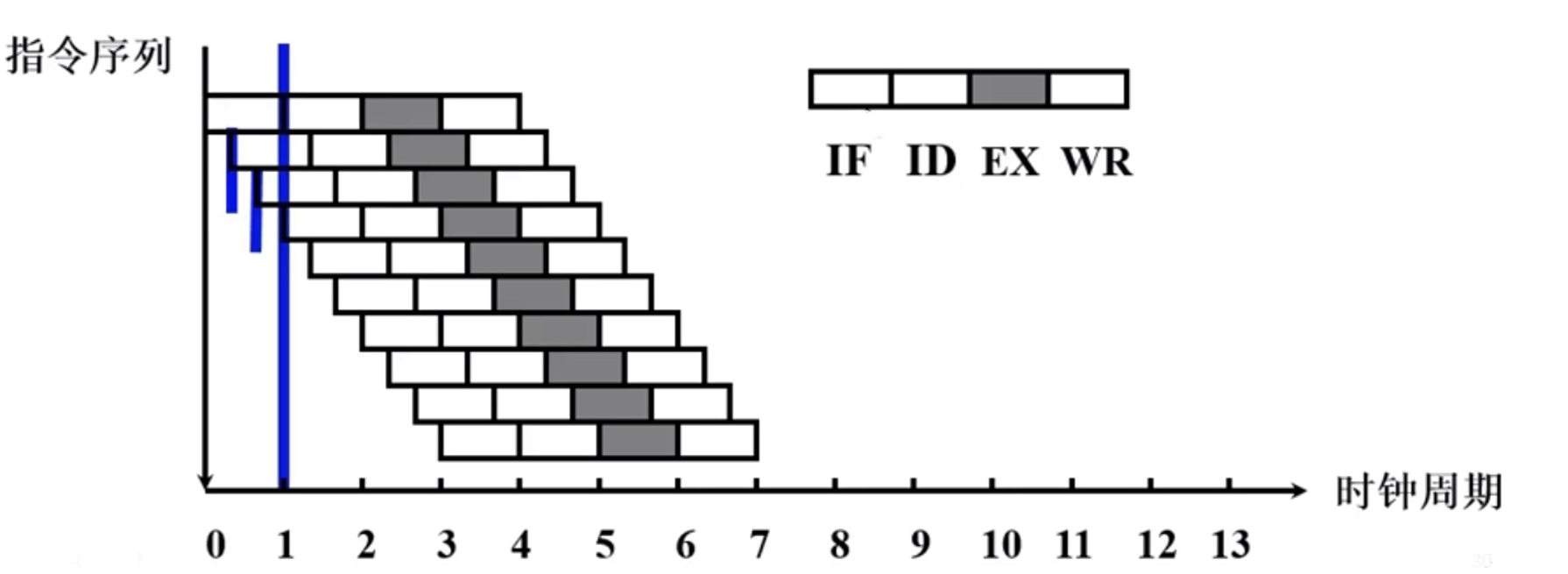

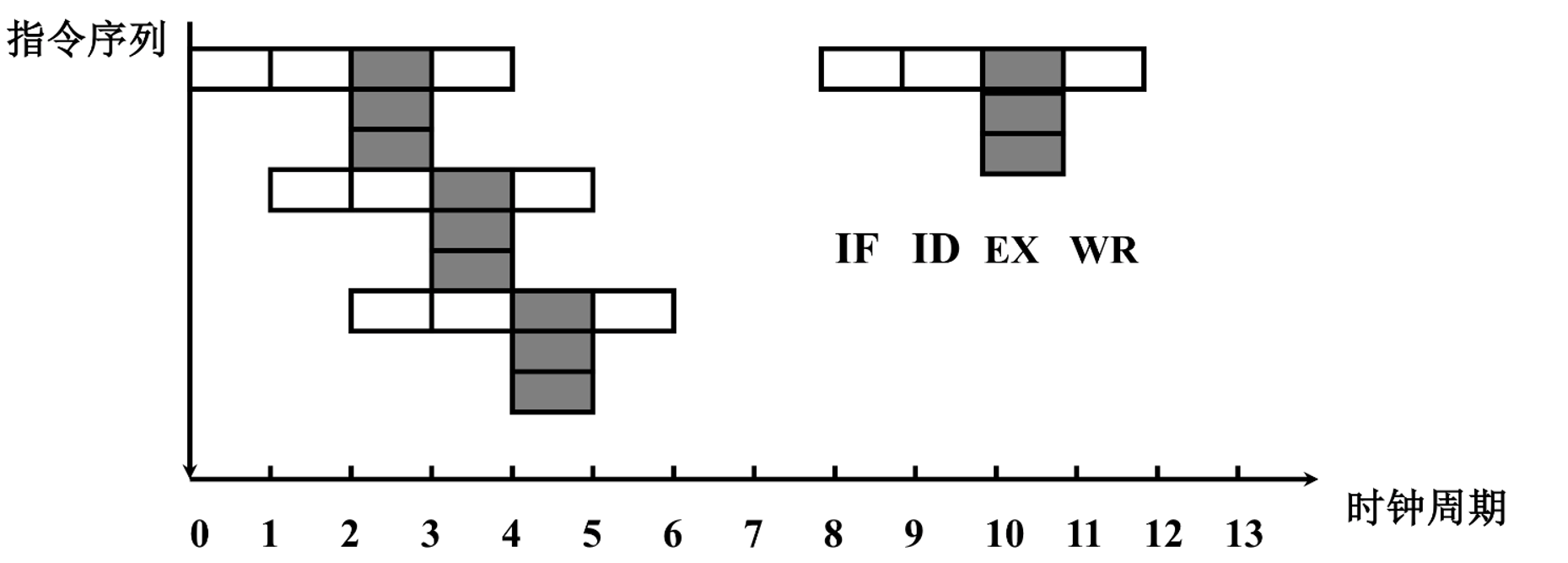

- 比如指令分为取指令、分析指令(译码和间址)、执行指令三个阶段,多条指令在执行时可以是顺序执行方式或流水线执行方式

- 顺序执行方式指在完成一条指令后,才开启下一条指令。设每阶段时间为t,共n条指令,则总时间为3nt

- 流水线执行方式指的是一条指令开启第i个阶段时(i=2,3),下一条指令开启第i-1个阶段。设每阶段时间为t,共n条指令,则总时间为2t+nt

- k级流水指的是,流水线有k个流水段。前面的例子,有三个执行阶段,即三级流水。

- 设计时,流水段的个数以最复杂的指令需要的阶段数为准,流水段的长度以最复杂的操作需要时间为准

流水线表示方法

- 采用时空图,横坐标为时间,各个流水段时间相等,纵坐标的每行对应一个流水段部件,每条指令形式上为斜线

- 也可以是横坐标为时间,各个流水段时间相等,纵坐标的每行对应每条指令,每个流水段部件形式上为斜线

流水线方式特点

- 把一个指令任务分解为多个子任务阶段,由不同功能部件并行完成

- 流水线每个功能段部件后有一个缓冲寄存器或锁存器,用来保存本段的执行结果,供下一段使用

- 流水线各功能段的时间尽量相等,防止堵塞和断流

- 流水线处理的尽量是连续任务

- 流水线需要装入和排空时间。前者是第一条任务进入流水线到完成的时间,后者是最后一条任务进入流水线到完成的时间。

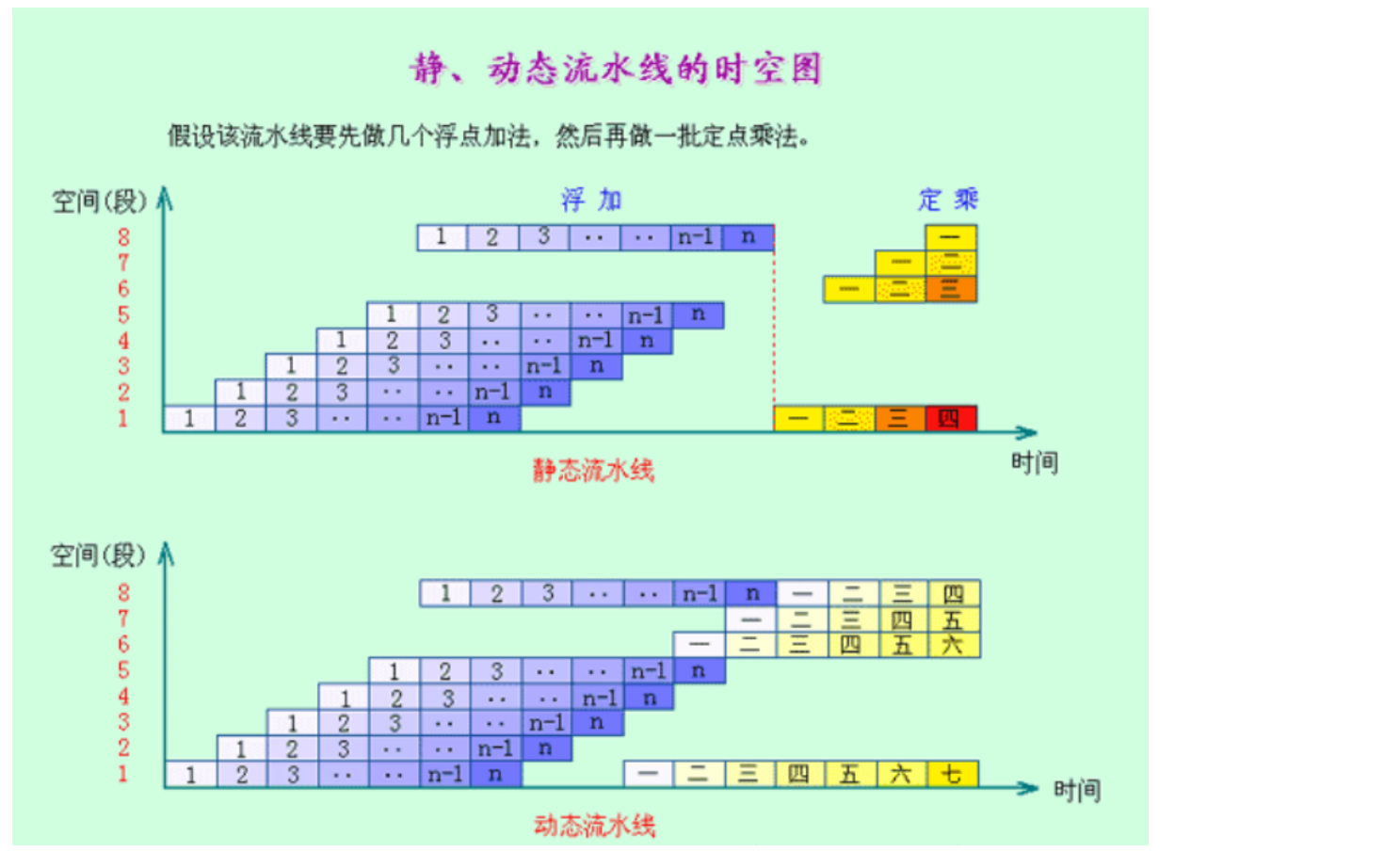

基本分类

- 按流水线使用级别分类

- 部件功能级:运算操作流水线

- 处理机级别:指令流水线

- 处理机间级别:宏流水线,涉及多个处理机

- 按功能分类

- 单功能:只能实现固定功能

- 多功能:通过各个流水段的不同连接方式,可以同时或不同时的实现多个功能

- 按连接方式(多功能流水线的分类)

- 静态流水线:各个段同时各自只能实现一个功能,多功能实现需要等任务排空后重连流水线,当连续输入不同运算时,静态流水线等同于顺序执行方式

- 动态流水线:各个段同时各自实现多个功能,效率高,控制复杂

- 下图是静态和动态流水时空图

- 按功能段是否有反馈信号

- 线性流水线:每段只经过一次,没有反馈回路

- 非线性流水线:有反馈回路,某些段多次经过,适合线性递归的运算

影响流水线的因素

- 流水线无法正确执行指令引起的阻塞、停顿,称为流水线冲突,或者冒险。

- 流水线冲突有三种:资源冲突、数据冲突、控制冲突

- 资源冲突(结构冒险)

- 指的是,不同流水段对硬件资源的竞争冲突

- 比如取指令和取数据都要访存

- 解决方法有

- 指令停顿:让后续指令暂停一个时钟周期

- 存储器分离:单独设置数据存储器和指令存储器

- 指令预取技术:适合访存周期短的情况,提前把指令取到缓存区

- 现代操作系统通过采用数据Cache和指令Cache分离的方式,避免资源冲突

- 数据冲突(数据相关、数据冒险)

- 指的是下一条指令用到当前指令计算结果确定

- 具体分为

- 写后读RAW:可能读到错误的旧值

- 读后写WAR:可能读到错误的新值

- 写后写WAW:可能先写新值,再写入旧值

- 解决方法有

- 后推法:设置时钟周期的暂停,比如硬件阻塞stall和软件插入NOP指令

- 数据旁路技术:对于RAW,设置专用通路,直接把ALU计算结果作为输入。

- 编译器优化相关指令,调整指令顺序。

- 控制冲突(控制相关、控制冒险)

- 指的是,下一条指令的地址由当前指令来确定,从而造成断流

- 如果不处理,将会存在控制损失,即跳转条件成立后,流水线原先按顺序执行的一些指令都是无效的。

- 解决方法有

- 对转移指令的分支进行预测,提前生成转移目标地址。静态(简单)预测总是预测条件不满足;动态预测根据历史执行情况,动态预测调整,预测准确率较高

- 预取转移成功和不成功两个控制流方向的目标指令

- 加快和提前形成条件码

- 提高转移方向的猜准率

性能指标

- 吞吐率TP

- 吞吐率指的是单位时间流水线完成的指令数量/输出结果数量

- 计算时考虑完成n条指令需要的时间,设

- 实际吞吐量为

- 加速比SP

- 加速比指的是,同一批任务,不使用流水线的时间比使用流水线的时间

- 实际加速比是

- 效率E

- 效率指的是流水线硬件设备的利用率

- 就是时空图中,工作时空区比总的时空区

- 实际效率为

超标量流水线

- 超标量流水线技术

- 每时钟周期并发多条独立的指令

- 配置多个功能部件,需要多个流水线

- 不能调整指令执行顺序,需要通过编译优化,把可并行的指令搭配起来

- 如下图是3个流水线并行工作

- 超流水线技术

- 又叫超流水技术

- 把一个时钟周期内继续分段;一个时钟周期内,一个部件使用多次

- 不能调整指令执行顺序,需要通过编译优化

- 如下图是一个时钟周期分为3段

- 超长指令字技术

- 由编译程序挖掘指令间潜在并行性

- 把多条可并行指令组合成一条具有多个操作码字段的超长指令字(可几百位)

- 采用多个处理部件,比如下图是三个

多处理器基本概念

SISD、SIMD、MIMD、向量处理器概念

本节介绍计算机体系结构的划分

- 单指令单数据流SISD

- 传统串行结构

- 包含一个处理器、一个存储器

- 使用指令流水方式,SISD处理器可采用多个功能部件,SISD存储器多采用多模块交叉存储器

- 单指令多数据流SIMD

- 一条指令,多个数据流,又叫数据级并行技术

- 包含一个控制器、多个处理单元,每个处理单元处理的数据不同,但处理的指令都是同一个

- 适合处理for循环处理数组或向量数据运算

- 多指令单数据流MISD:不存在

- 多指令多数据流MIMD

- 多条指令,多个数据流,线程级(或线程级以上)并行技术

- 分为

- 多计算机系统(消息传递MIMD):各系统有各自的存储器、独立的主存空间,通过消息传递进行数据传输

- 多处理器系统(共享存储MIMD):全称是共享存储多处理器SMP,共享地址空间,各处理器通过共享变量通信,通过存取指令访问存储器,

- 向量处理器

- SIMD的变种

- 实现了可直接操作向量指令集的CPU

- 理念是把存储器收集的数据按顺序放到向量寄存器中,流水方式依次操作,结果写回寄存器

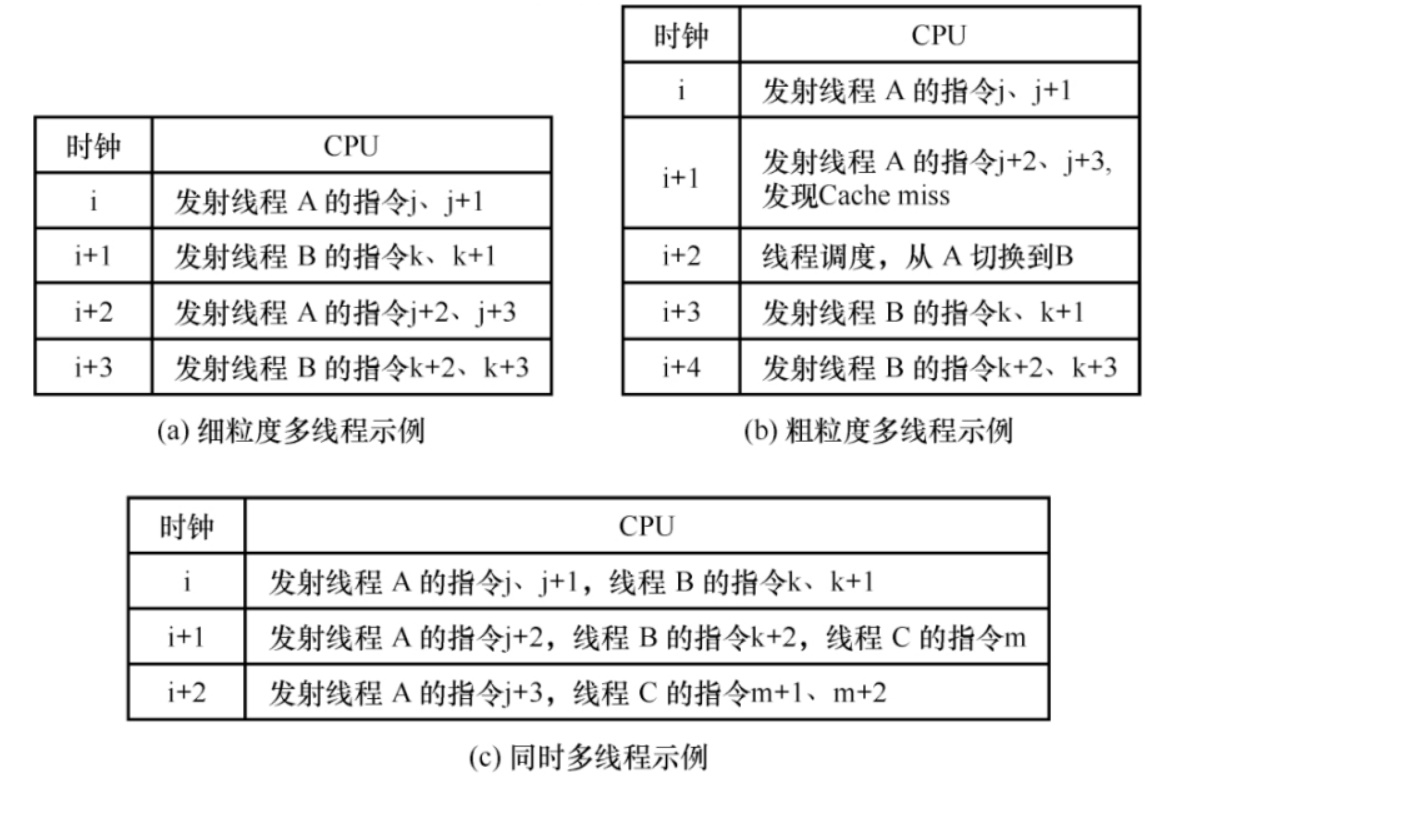

硬件多线程基本概念

- 传统CPU线程切换开销较大,需要和存储器交换数据

- 支持硬件多线程的CPU,每个线程有独立的通用寄存器组、PC,线程切换只需要激活选中的寄存器

- 硬件多线程有3种实现方式

- 细粒度多线程

- 各线程间指令无关

- 每个时钟周期切换线程

- 粗粒度多线程

- 只在遇到阻塞时才切换线程,如Cache缺失

- 流水线需要清空和重装,切换线程开销高

- 同时多线程

- 又叫SMT,例如因特尔处理器的超线程

- 同一时钟周期,不同线程多条指令同时执行

- 同时实现指令级并行和线程级并行

- 细粒度多线程

- 下图是硬件多线程3种实现的示例图

多核处理器基本概念

- 多个处理单元(核)集中到一个CPU

- 每个核可以有各自的Cache,也可以共享Cache

- 各核是对称的,共享主存,可以认为多核处理器是SMP的简化版

- 多核处理器的多线程是并行的(同一时刻多个线程运行),而单核的多线程是并发的(交错执行,但同一时刻只有一个线程执行)

共享内存多处理器SMP的基本概念

- 多个处理器共享一个物理地址空间,通过存取指令访问存储器

- 处理器间的通信通过存储器的共享变量

- 分类有

- 统一存储访问(UMA)多处理器

- 每个处理器访存时间接近,所有CPU的地位是对称的

- 根据处理器和共享存储的连接方式,分为基于总线、基于交叉开关网络、基于多级交换网络连接几种多处理器

- 非统一存储访问(NUMA)多处理器

- 某些处理器访存请求较快完成

- 根据处理器是否带一致性高速缓存,分为NC-NUMA和CC-NUMA

- 统一存储访问(UMA)多处理器

- 共享变量可以通过加锁的方式实现互斥访问